MicroEJ Architecture

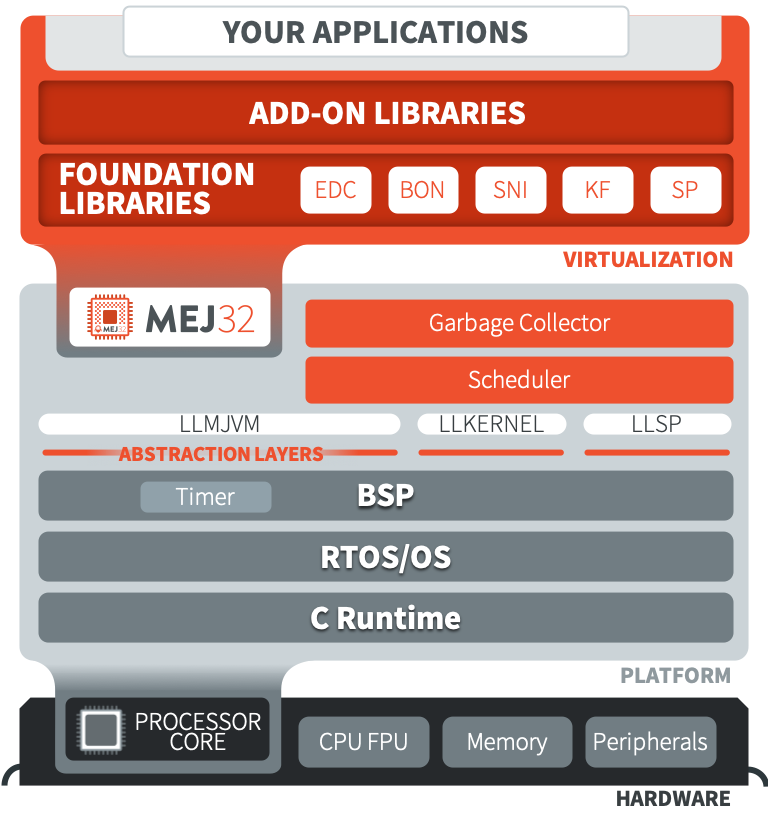

MicroEJ Architecture features the Core Engine built for a specific instructions set (ISA) and compiler.

The Core Engine is a tiny and fast runtime associated with a Scheduler and a Garbage Collector.

MicroEJ Architecture provides implementations of the following Foundation Libraries :

Embedded Device Configuration (see [EDC]).

Beyond Profile (see [BON]).

Simple Native Interface (see [SNI]).

Kernel & Features (see [KF]).

Shielded Plug (see [SP]).

The following figure shows the components involved.

MicroEJ Architecture Modules

Three Low Level APIs allow the MicroEJ Architecture to link with (and port to) external code, such as any kind of RTOS or legacy C libraries:

Simple Native Interface (see [SNI])

Low Level Core Engine (see LLMJVM)

Low Level Shielded Plug (see LLSP)

For further information on Architecture installation and releases, you can check these chapters: